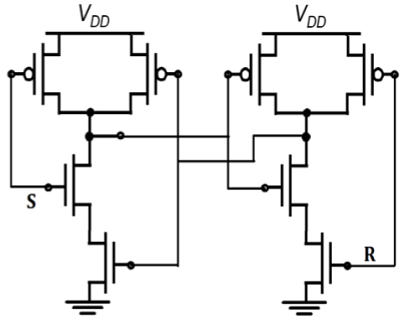

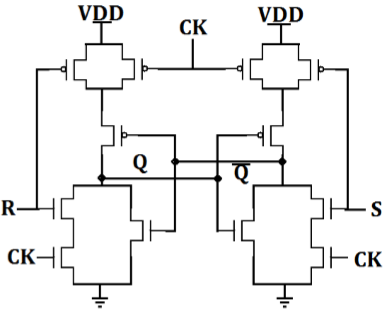

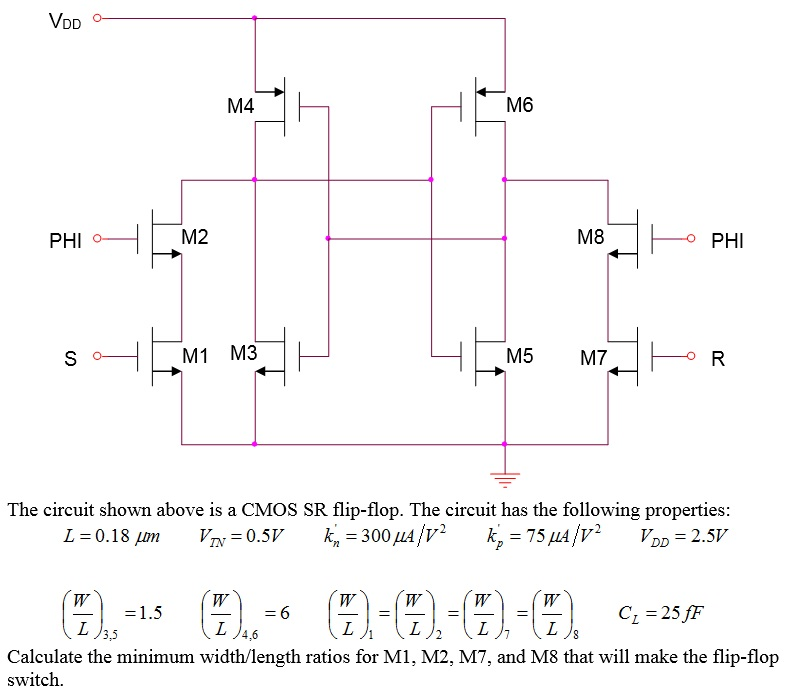

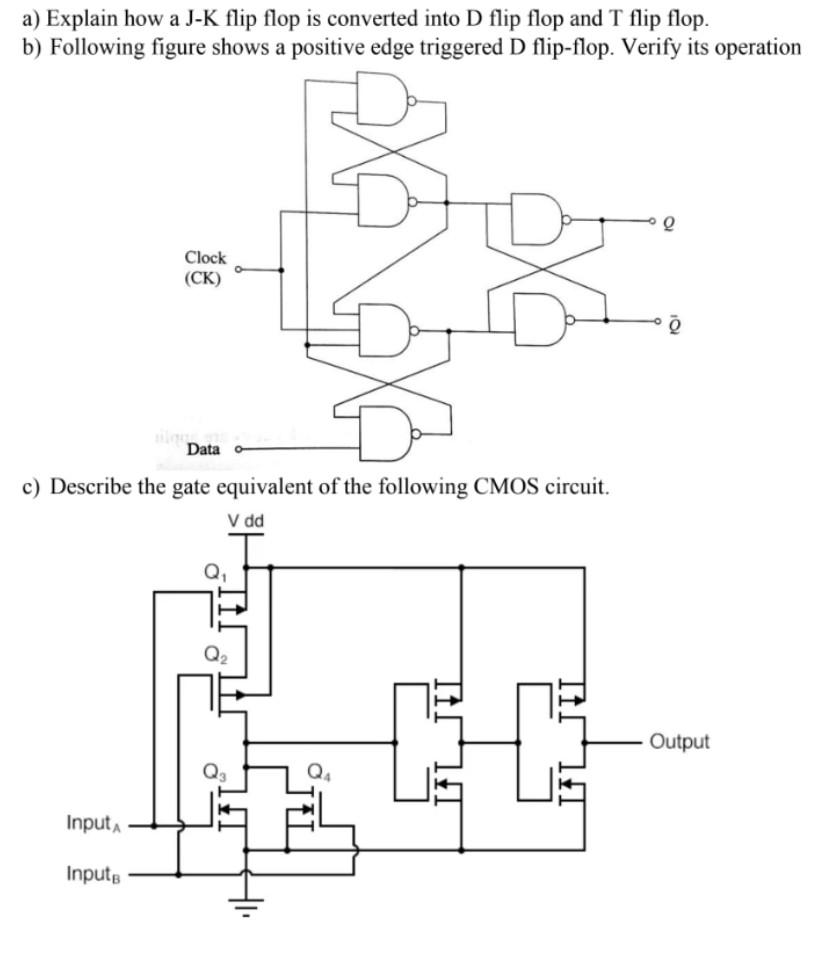

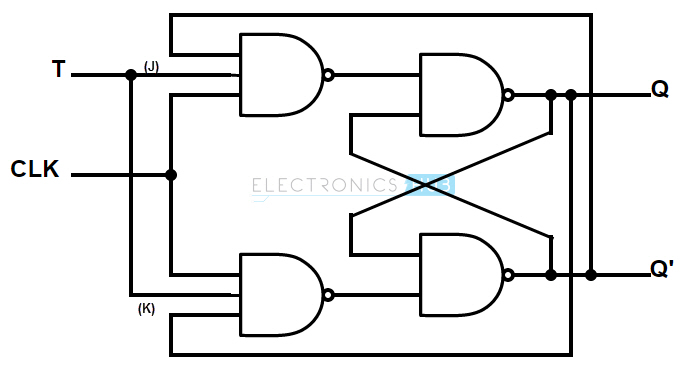

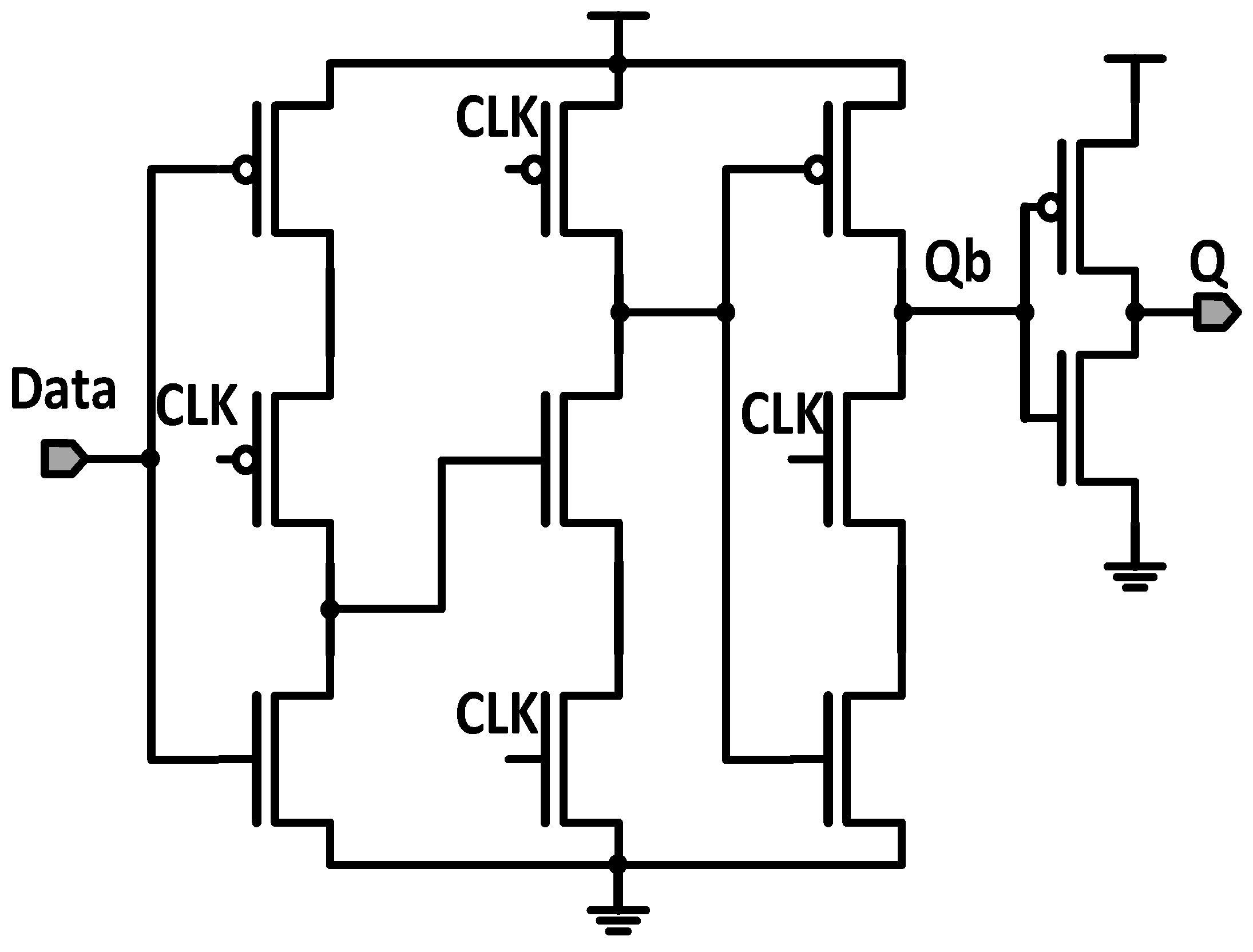

Figure2. (a)The Design of CMOS DET flip-flop (b) A Modified design of... | Download Scientific Diagram

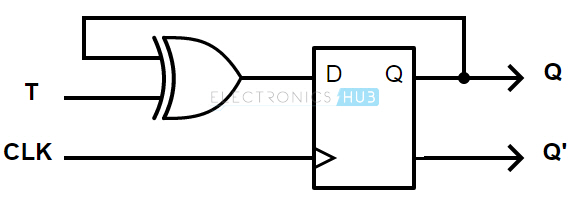

Design and analysis of ultra‐low power 18T adaptive data track flip‐flop for high‐speed application - Kumar Mishra - 2021 - International Journal of Circuit Theory and Applications - Wiley Online Library

Electronics | Free Full-Text | Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips